一、寫在前面

在SMT已占據主流的今天,DIP插件仍然頻繁出現在電源、功率、連接器、繼電器、鋁電解電容、變壓器、LED模組等場景。它既不是“落后工藝”,也不是“萬能方案”,而是一把仍需熟練掌握的“老刀”。1943科技從量產角度梳理DIP的核心優缺點,供工藝、設備、品管、采購同事參考。

二、優點

-

機械強度高

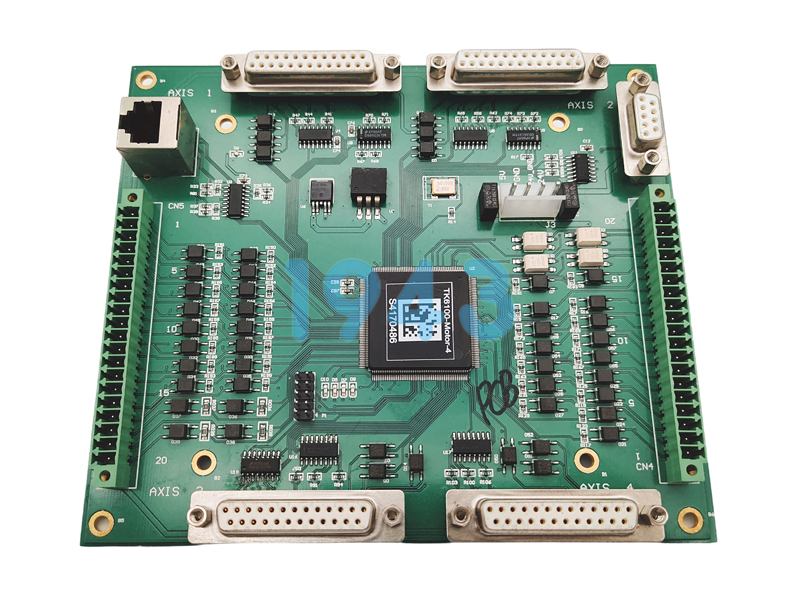

元件引腳貫穿PCB,焊接后形成“鉚釘”效應,抗彎曲、抗振動、抗熱沖擊優于純表貼。汽車電子、工業控制、大功率LED 對可靠性要求高,DIP仍是首選封裝之一。 -

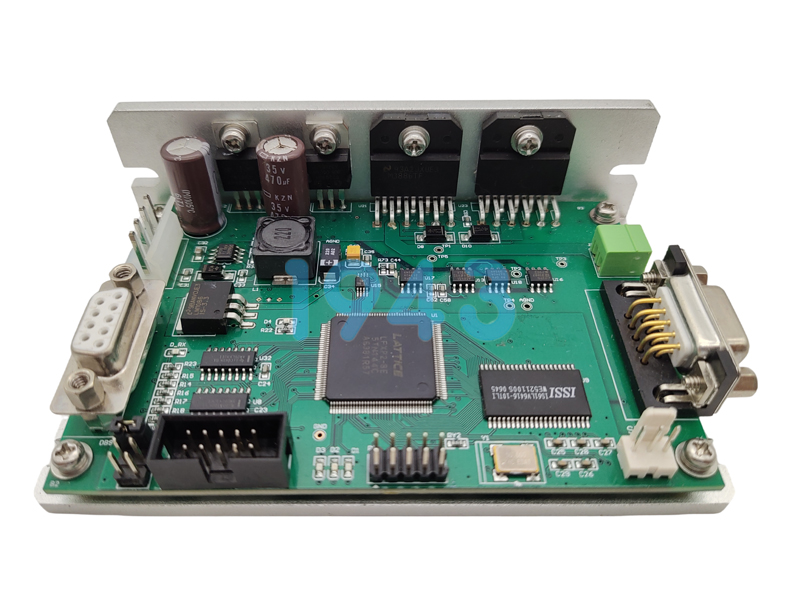

功率與散熱友好

TO-220、TO-247 等功率器件引腳粗、導熱墊大,可直接鎖螺絲加散熱片;配合通孔,熱量可沿銅箔快速擴散。SMD想做到同等散熱,需要大面積銅皮、過孔陣列或金屬基板,成本反而更高。 -

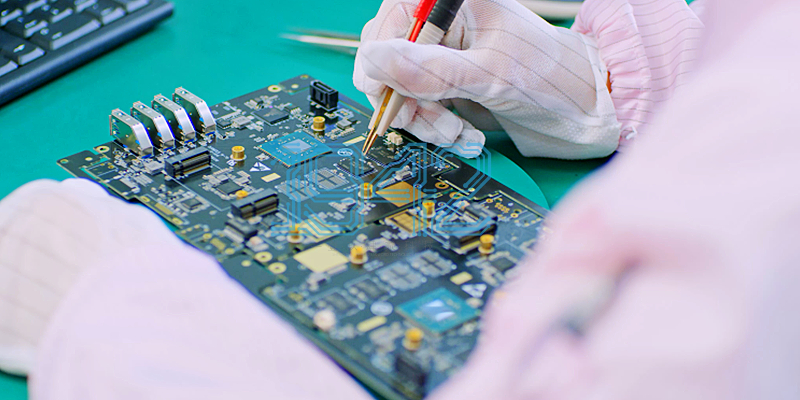

手工焊接/返修門檻低

波峰焊、選擇性波峰焊、手工焊、浸焊都能用;烙鐵一夾、吸錫器一捅即可拆換。小批量、樣機、售后維修場景下,DIP可顯著降低人力與時間成本。 -

通孔可兼做測試點

引腳外露,ICT夾具探針直接戳引腳即可,無需額外測試焊盤。對ATE覆蓋率有硬性要求的板子,這一優勢常被忽視卻極其實用。 -

供應鏈彈性大

大量老牌料號常年不缺貨,價格穩定;部分國產功率器件、繼電器、連接器只有DIP封裝。遇到缺芯潮,SMT料漲價斷貨,DIP往往還能買到現貨。 -

設備投入低

插裝機比貼片機便宜,維護簡單;波峰焊爐也比回流焊爐寬容度高,對profile不敏感。小廠或外發臨時加線,DIP線體可在一周內拉通。

三、缺點

-

組裝密度低

2.54 mm 標準間距起步,占板面積是同功能SMD的3~10倍。手機、筆電、可穿戴等對空間斤斤計較的產品,DIP幾乎絕跡。 -

自動化程度受限

立式、臥式插裝機速度一般 < 15 k件/小時,遠低于高速貼片機 80~150 k件/小時;異形件仍需人工補插。大批量消費級產品若強行用DIP,瓶頸明顯。 -

波峰焊缺陷率高

連錫、漏焊、透錫不良、陰影效應、助焊劑殘留,每一項都能把直通率拉低幾個點。治具開窗、噴霧角度、鏈速、預熱斜率需反復DOE才能收斂。 -

板子層數與成本倒掛

通孔會吃掉走線空間,迫使層數增加;過孔塞油、樹脂塞孔又增加流程。高密度板若強行混裝DIP,往往“省下的器件錢全花在PCB上”。 -

高頻性能差

引腳電感、寄生電容大,>50 MHz 的信號完整性明顯劣于SMD無引腳封裝。RF、高速SerDes、DDR 等場合需慎重。 -

環保壓力

波峰焊比回流焊更耗錫、耗電、耗助焊劑,且錫渣多;若使用水洗助焊劑,廢水COD 高。出口歐盟需額外計算碳排放與REACH 合規成本。

四、如何揚長避短

-

混裝策略

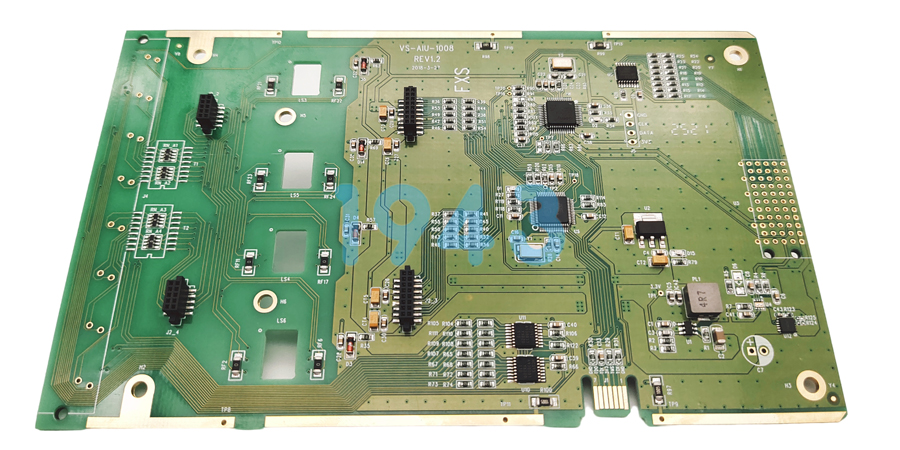

功率器件、連接器、電解電容用DIP,小信號、高速器件用SMD;拼板時把DIP集中在同一面,一次性過波峰焊,減少治具翻轉。 -

選擇性波峰焊

對局部DIP區域開小窗,避免整板浸泡;配合氮氣保護,錫渣量下降30 %以上。 -

預成型錫片+壓接

部分功率器件可取消波峰焊,改用預成型錫片+回流焊一次完成,既保留通孔強度,又避免波峰焊缺陷。 -

設計端提前干預

引腳長度、孔徑、焊環寬度、阻焊開窗、bottom-side 貼片避讓,都在設計評審時固化;不要等到SOP階段再改封裝。 -

備料策略

DIP料體積大、價格低,可一次性多備半年庫存,減少因MOQ帶來的呆滯風險;同時與SMD料做BOM“雙封裝”備案,缺貨時可快速切換。

五、結語

DIP插件不是“情懷”,也不是“累贅”。在功率、散熱、可靠性、維修性、供應鏈彈性上,它有不可替代的優勢;在密度、自動化、高頻、環保上,它又必須被SMT替代或優化。作為SMT貼片加工廠,唯有把DIP當作一種常規工藝,持續積累治具、程序、參數、案例,才能在客戶提出“混裝”“異形件”“功率板”需求時,給出既快又省的完整方案。

2024-04-26

2024-04-26