在工業自動化與精密制造領域,多軸運動控制器的性能直接決定了設備的響應速度與定位精度。作為其核心載體,PCBA的布局設計需兼顧信號完整性、電源穩定性及制造可行性。尤其在高速數字信號與模擬信號共存的場景下,如何通過優化布局減少信號間串擾,成為PCBA加工中的核心技術挑戰。

一、高速信號串擾的成因分析

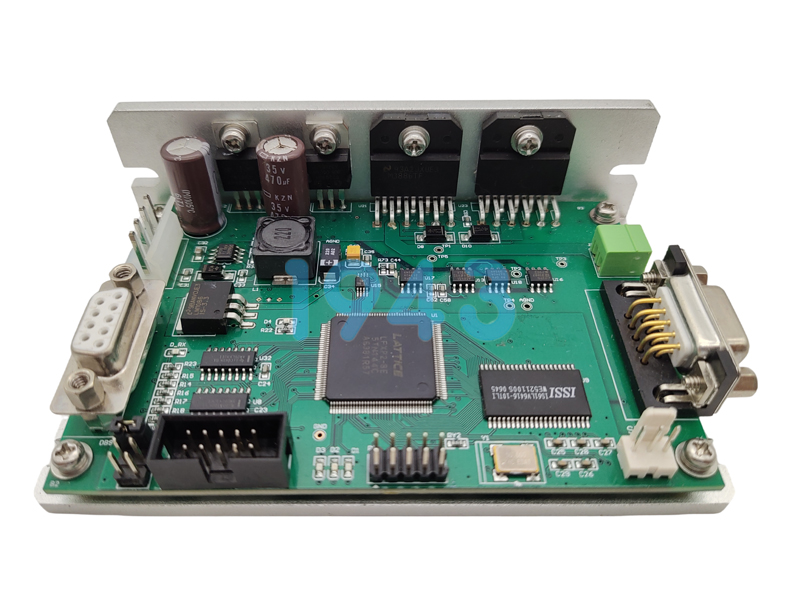

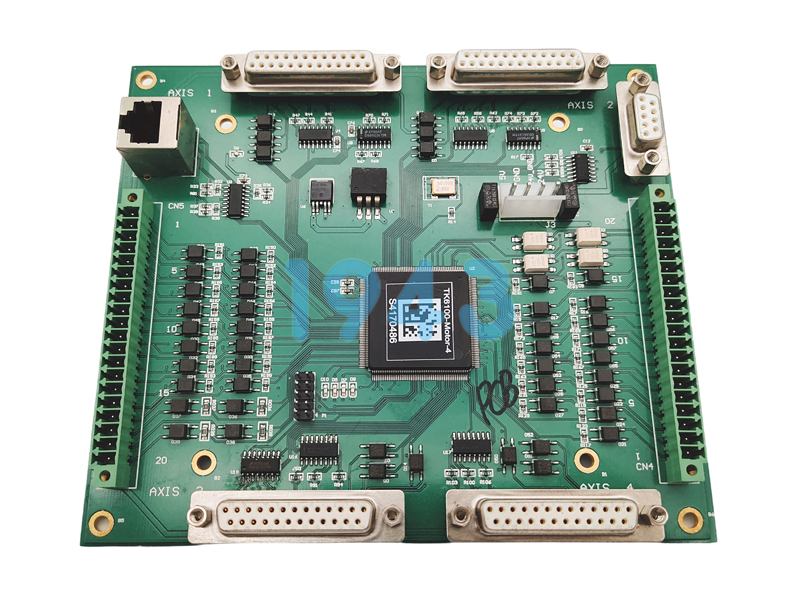

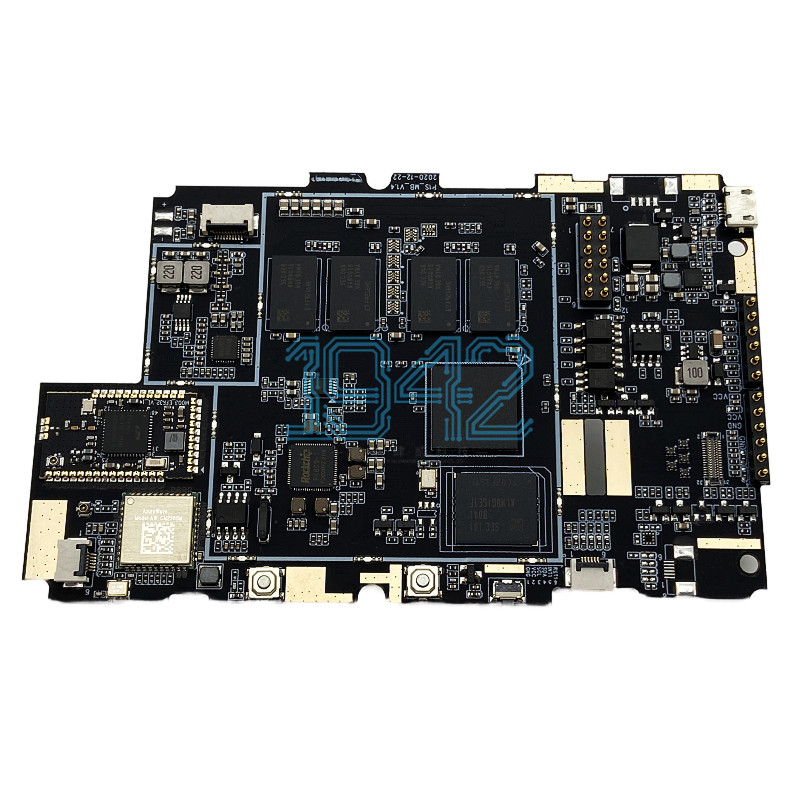

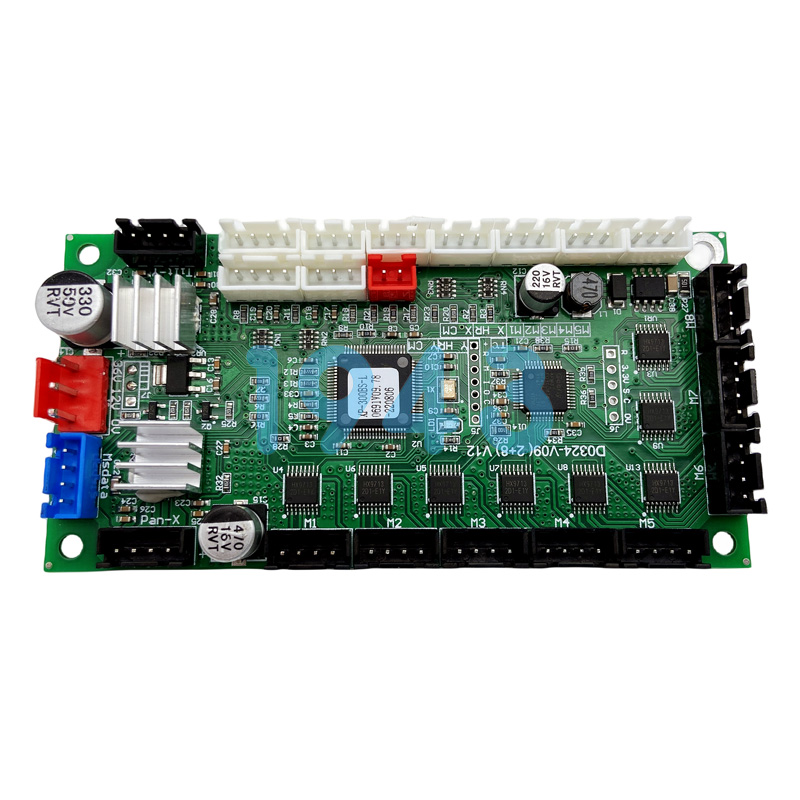

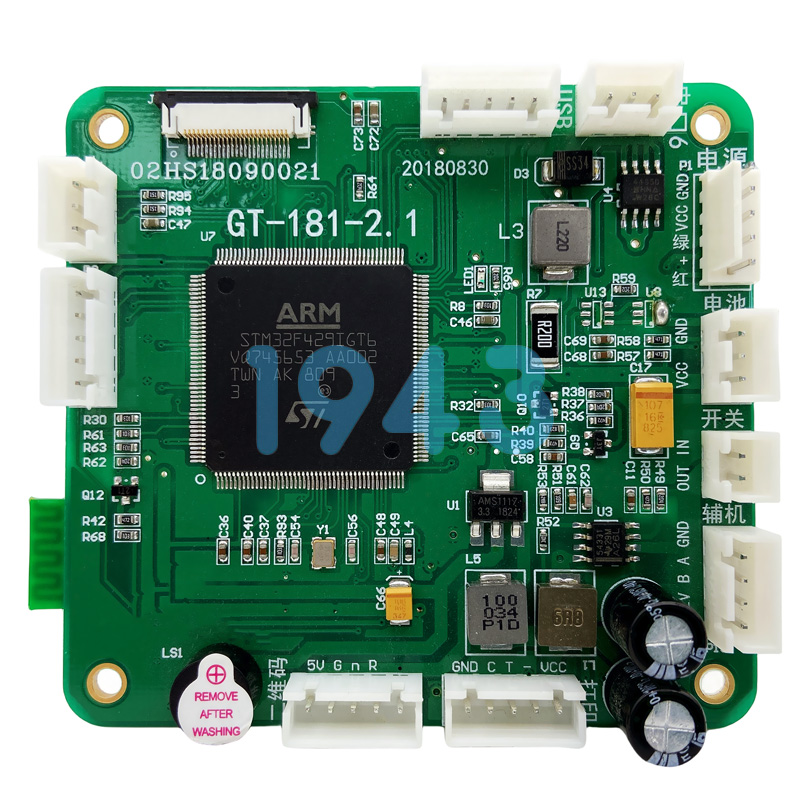

多軸運動控制器PCBA通常集成FPGA/DSP芯片、高速串行總線(如EtherCAT、PCIe)、高精度ADC/DAC及功率驅動電路。當信號速率超過500Mbps時,以下因素可能導致串擾:

- 耦合效應:相鄰信號線間的容性耦合與感性耦合,導致信號邊沿的電壓波動;

- 電源噪聲:功率電路(如電機驅動模塊)產生的紋波通過電源/地平面傳導至敏感信號;

- SMT貼片工藝偏差:元件貼裝精度不足可能導致阻抗失配,加劇反射與串擾。

二、布局優化核心原則

1. 信號分層與隔離設計

- 高速信號專屬層:將PCIe、SERDES等高速差分對布置在內層,利用相鄰完整地平面作為參考,減少輻射與耦合。

- 模擬/數字分區:通過地線隔離帶或物理分割將ADC/DAC與數字電路隔離,避免數字噪聲通過電源/地平面污染模擬域。

2. 關鍵信號路徑優化

- 3W原則:高速信號線間距≥3倍線寬,差分對間距≤1倍線寬以維持共模抑制比。

- 蛇形走線控制:在SMT貼片區域避免蛇形線,防止因焊盤不對稱導致的阻抗突變。

- 端接策略:在FPGA輸出端集成源端串聯電阻(如22Ω),匹配傳輸線特性阻抗(通常為50Ω或100Ω)。

3. 電源與地平面優化

- 局部電源島:為FPGA核心電壓(如1.0V)創建獨立電源平面,通過磁珠與主電源隔離。

- 地平面完整性:確保高速信號參考地平面無斷裂,SMT貼片焊盤通過多個過孔連接至地平面。

4. 元件布局與散熱協同

- 熱源分散:將功率器件(如MOSFET)與敏感芯片間距保持≥10mm,利用電路板加工中的金屬基板或熱過孔散熱。

- BGA扇出優化:FPGA等BGA器件采用“先扇出后換層”策略,減少高速信號換層次數。

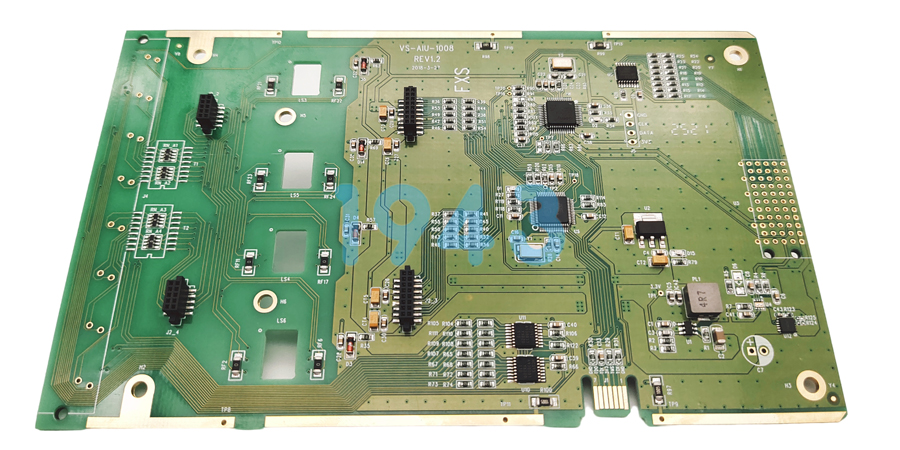

三、PCBA加工與SMT貼片工藝協同

- 阻抗控制:在電路板加工階段,通過疊層設計與介質材料選擇(如FR408HR,Dk=3.64),實現50Ω±10%的阻抗控制。

- SMT貼片精度:采用高精度貼片機,確保0402/0201元件無偏移,避免因元件錯位導致的信號短路。

- 選擇性鍍金:對高速連接器焊盤進行ENEPIG(化學鎳鈀金)處理,提升可焊性并減少接觸電阻。

四、驗證與測試

- 時域反射測試(TDR):在PCBA加工后,使用TDR儀器驗證關鍵信號線的阻抗連續性。

- 近端串擾(NEXT)測試:通過矢量網絡分析儀測量相鄰信號線的耦合度,確保NEXT≤-30dB@1GHz。

- 高溫反偏測試:在85℃環境下對FPGA I/O進行24小時老化測試,篩選潛在焊接缺陷。

結語

多軸運動控制器PCBA的布局優化需貫穿設計、加工與測試全流程。通過信號分層隔離、電源完整性設計及SMT貼片工藝控制,可顯著降低高速信號串擾,提升系統信噪比(SNR)至60dB以上。隨著5G+工業互聯網的融合,對PCBA加工的精度與可靠性要求將進一步提升,需結合HDI(高密度互連)技術與AI輔助設計工具,實現更緊湊、更抗干擾的布局方案。

因設備、物料、生產工藝等不同因素,內容僅供參考。了解更多smt貼片加工知識,歡迎訪問深圳smt貼片加工廠-1943科技。

2024-04-26

2024-04-26