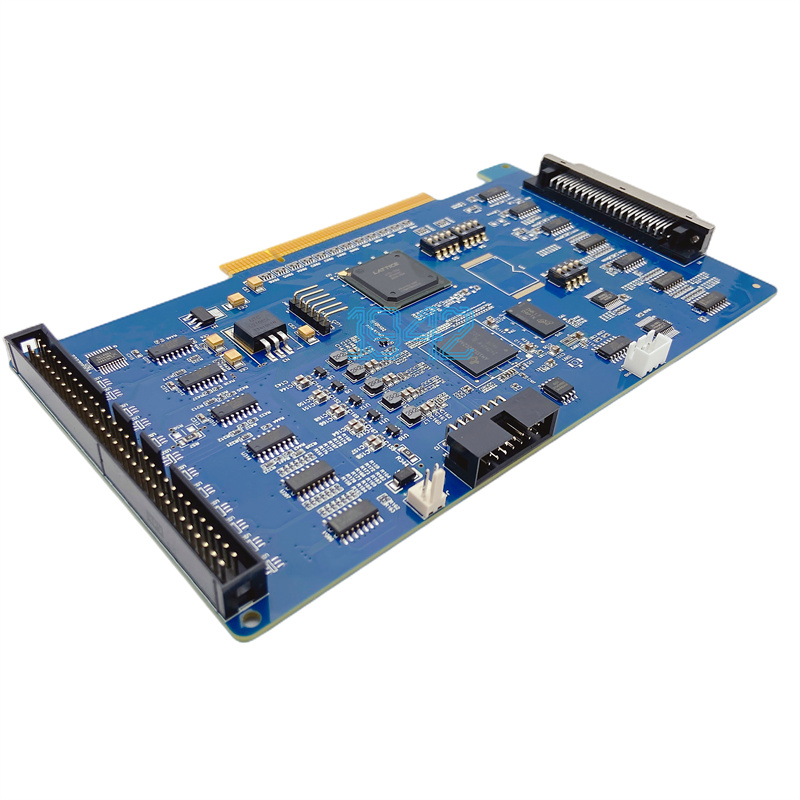

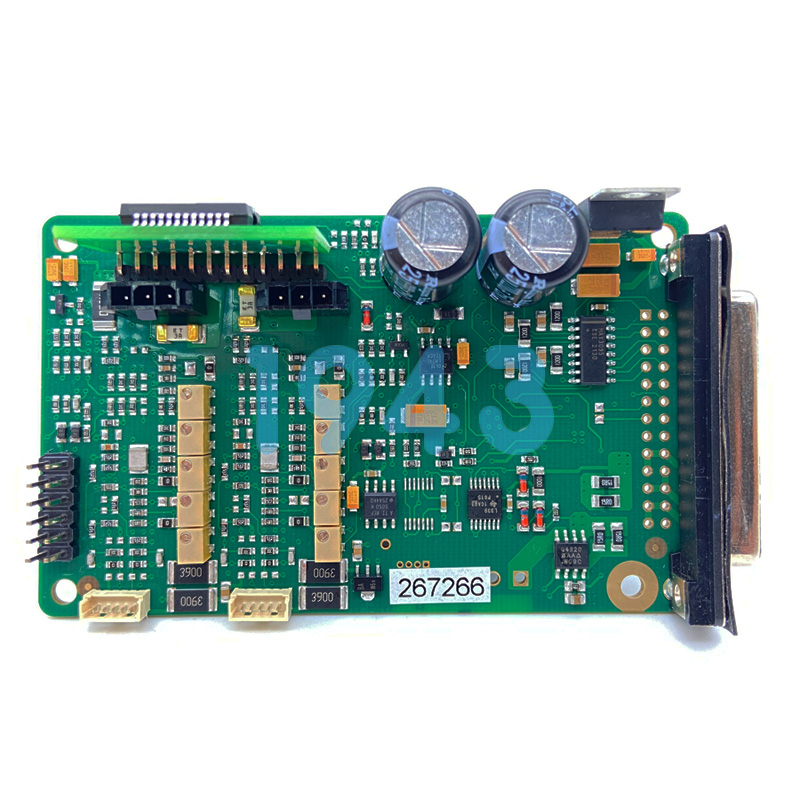

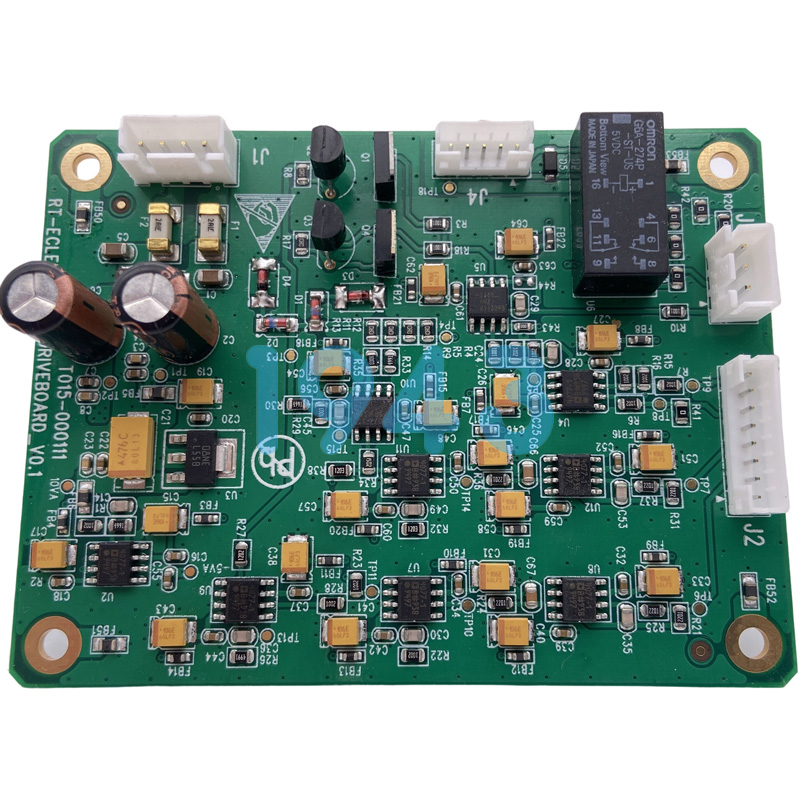

在工業以太網領域,PoE(PoweroverEthernet)模塊作為實現電力與數據信號共纜傳輸的核心部件,其可靠性直接影響工業網絡的穩定性。在PoE模塊的PCBA加工過程中,SMT貼片工藝環節對焊點質量提出了極高要求。其中,電遷移現象作為導致焊點失效的重要因素之一,與PCB銅箔粗糙度之間存在顯著相關性,成為當前SMT焊接工藝優化的關鍵研究方向。

一、電遷移現象的機理與危害

電遷移是指在電流驅動下,金屬原子沿電子流動方向發生遷移的物理現象。在PoE模塊的電源傳輸路徑中,焊點與PCB銅箔界面處的金屬間化合物(IMC)層及焊料合金,在持續電流作用下易發生原子遷移,導致焊點局部出現空洞、裂紋甚至斷裂。對于PoE模塊而言,其工作時需承載48V直流電壓及較大電流(如IEEE802.3bt標準下可達90W功率),電流密度集中的焊點區域成為電遷移高發區。PCB銅箔表面粗糙度通過影響焊點界面的微觀結構,直接改變電流分布均勻性與界面結合力。粗糙度過高時,銅箔表面的凸凹結構會導致焊點內部形成應力集中點,同時增大電流流經界面時的有效路徑電阻,加劇局部發熱與原子遷移速率;粗糙度過低則可能降低銅箔與焊料的浸潤性,導致界面結合強度不足,為電遷移提供初始缺陷條件。

二、PCB銅箔粗糙度對電遷移的影響機制

1.界面微觀結構差異

工業PCB常用的電解銅箔(ElectrodepositedCopper,ED銅箔)表面通常存在微米級粗糙度(Rz值5-15μm),其粗化層通過電化學處理形成,旨在增強與基材及焊料的結合力。而壓延銅箔(RolledAnnealedCopper,RA銅箔)表面粗糙度較低(Rz值1-5μm),多用于高頻或高可靠性場景。研究表明,當銅箔表面存在尖銳凸起或深凹坑時,焊點凝固過程中易在該處形成IMC層厚度不均現象,凸起部位的IMC層通常更薄,成為電遷移的優先起始點。

2.電流密度分布特性

在SMT貼片加工中,焊點與銅箔的界面接觸面積隨銅箔粗糙度增加而增大,但電流密度分布會因表面不規則性出現局部集中。通過有限元仿真分析發現,當銅箔表面粗糙度Rz值超過10μm時,焊點邊緣區域的電流密度較平整表面高出30%-50%,這種不均勻分布會加速該區域的原子遷移,導致焊點邊緣優先出現空洞缺陷。

3.熱機械應力協同作用

PoE模塊在工作時,PCB與元器件的熱膨脹系數(CTE)差異會在焊點界面產生周期性熱應力。粗糙的銅箔表面會改變焊點的應力傳遞路徑,在凸起部位形成應力集中區。當熱應力與電遷移效應疊加時,界面處的原子遷移速率可提升2-3倍,顯著縮短焊點的失效周期。

三、基于銅箔粗糙度的電遷移抑制策略

1.銅箔材料優選與表面處理

在PoE模塊的PCB設計階段,需根據電流承載需求選擇適配的銅箔類型:對于大電流傳輸的電源路徑,建議采用Rz值6-8μm的中粗糙度電解銅箔,在保證焊料浸潤性的同時避免過度粗糙導致的界面缺陷;對于信號傳輸路徑,可選用低粗糙度銅箔以降低高頻損耗。此外,采用表面鍍覆工藝(如鍍鎳金、鍍銀)可改善銅箔表面平整度,鍍覆層厚度需控制在5-8μm,以平衡導電性與界面結合力。

2.SMT焊接工藝優化

在SMT加工的回流焊環節,需針對銅箔粗糙度調整溫度曲線:對于高粗糙度銅箔,適當降低峰值溫度(建議控制在245±5℃)并延長保溫時間,促進焊料對銅箔凹坑的充分填充,減少界面空洞;對于低粗糙度銅箔,需提高升溫速率(1.5-2℃/s)以確保焊料快速鋪展,避免因浸潤不足導致的虛焊風險。同時,選擇含Ni、Co等微量元素的焊料合金(如Sn-3.0Ag-0.5Cu-0.05Ni),可通過細化IMC層晶粒結構,提升焊點抗電遷移能力。

3.焊點形態與結構設計

在SMT貼片過程中,通過優化鋼網開口尺寸(建議比焊盤尺寸縮小5%-10%)與印刷壓力,控制焊點的焊料量與高度,使焊點形成45°-60°的理想潤濕角。對于電源路徑的關鍵焊點,可設計“淚滴”狀焊盤結構,增大焊點與銅箔的接觸面積,分散電流密度與熱應力。此外,在PCB布局時,避免將大電流焊點布置在PCB彎曲變形敏感區域,減少機械應力對電遷移的促進作用。

四、結語

在工業以太網PoE模塊的PCBA加工中,SMT焊接環節的電遷移問題與PCB銅箔粗糙度存在顯著的相關性。通過深入研究銅箔表面微觀結構對焊點界面特性的影響機制,結合材料優選、工藝優化與結構設計等多維度措施,可有效抑制電遷移現象,提升PoE模塊的長期可靠性。隨著工業互聯網對設備穩定性要求的不斷提高,針對SMT加工中材料特性與失效機理的相關性研究,將持續為高可靠性PCBA的制造提供技術支撐。

因設備、物料、生產工藝等不同因素,內容僅供參考。了解更多smt貼片加工知識,歡迎訪問深圳PCBA生產加工廠家-1943科技。

2024-04-26

2024-04-26