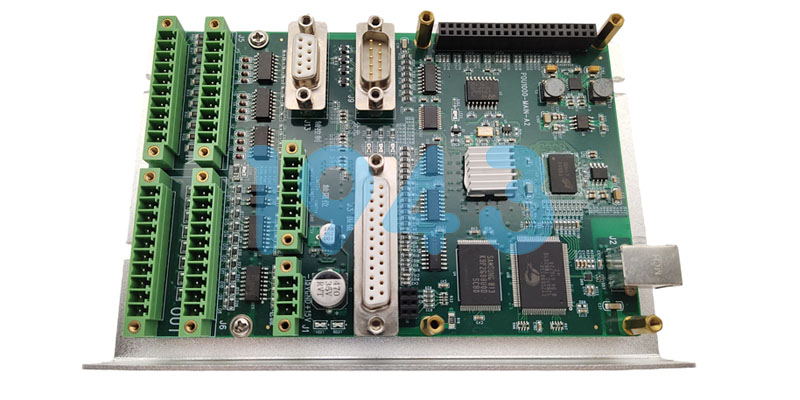

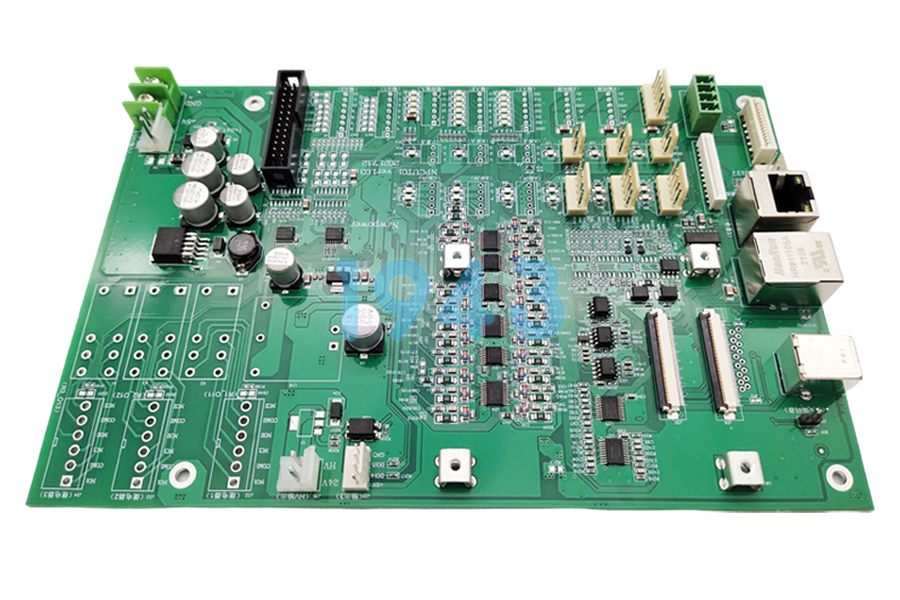

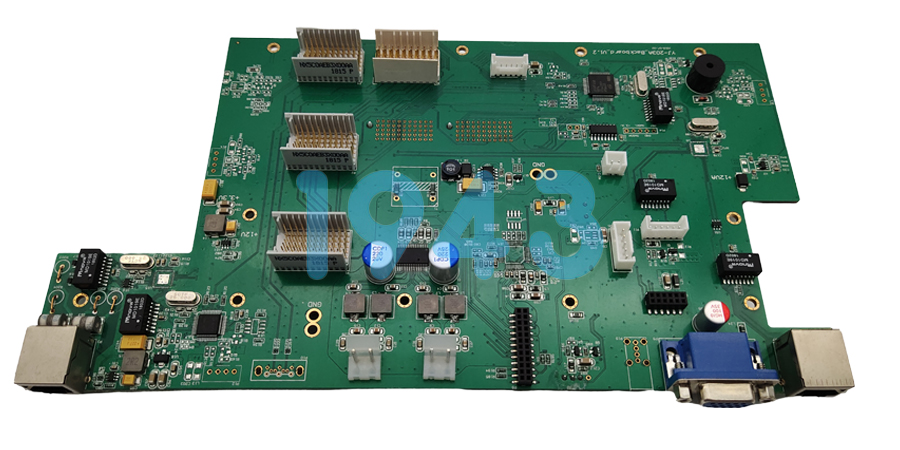

自動駕駛域控制器作為汽車的“超級大腦”,其PCBA電路板承載著海量傳感器數據的融合處理與實時決策。在這個高速數據交互的核心地帶,信號完整性(SI) 設計直接決定了系統的穩定性、可靠性和性能上限。尤其在制造環節PCBA加工中,對高速總線標準的嚴格遵循是保障最終產品品質的基石。以下是在設計時必須重點滿足的關鍵高速總線標準:

PCI Express (PCIe):

-

應用: 域控制器內部核心處理器(SoC/CPU)、AI加速器、大容量存儲(NVMe SSD)、高性能傳感器接口之間的超高速互連。當前主流是PCIe Gen 4 (16 GT/s),正向PCIe Gen 5 (32 GT/s) 和 Gen 6 (64 GT/s) 邁進。

-

SI設計關鍵點:

-

極嚴格的差分對內偏移(Skew)和對間偏移控制: 需精確匹配差分對長度,并嚴格控制不同通道間的長度差異。

-

低損耗板材選擇: 高頻下介質損耗成為主要因素,需選用如M7級別或更優的低損耗/超低損耗(Df值小)板材。

-

精確阻抗控制: 通常要求85Ω (+/-5% 或更嚴) 差分阻抗,貫穿整個鏈路(芯片封裝、PCB走線、連接器)。

-

優化的過孔設計: 采用背鉆(Stub Removal)、微孔(HDI技術)減小過孔殘樁(stub)效應,降低反射和損耗。

-

電源完整性(PI)協同設計: PCIe對供電噪聲極其敏感,需極低阻抗的電源分配網絡(PDN),搭配高性能去耦電容(靠近芯片放置,多種容值組合)。

-

高速以太網 (Multi-Gigabit Ethernet):

-

應用: 連接攝像頭、雷達、激光雷達等傳感器,以及域控制器之間的通信(如中央計算平臺)。主流包括1000BASE-T1 (1Gbps)、10GBASE-T1 (10Gbps),未來將向更高速率演進。

-

SI設計關鍵點:

-

差分信號完整性: 遵循IEEE 802.3標準規定的發送端(Tx)和接收端(Rx)信號質量要求(如眼圖模板、抖動、回波損耗、插入損耗)。

-

連接器與線纜建模: 必須考慮車載連接器、線束的阻抗匹配和損耗,將其納入端到端通道仿真模型。

-

EMI/EMC考量: 高速差分線是強輻射源,需精心設計參考平面、使用共模扼流圈、優化屏蔽層連接,滿足嚴苛的車規EMC要求(如CISPR 25)。

-

隔離設計: 常需電氣隔離以滿足功能安全和地噪聲隔離要求,隔離器件的信號完整性需特別關注。

-

LPDDR4/LPDDR5/LPDDR5X:

-

應用: 為高性能SoC提供大帶寬、低功耗的內存訪問。

-

SI設計關鍵點:

-

超嚴格的時序預算: 極高的時鐘頻率和數據速率(LPDDR5可達6400 Mbps以上)要求極低的走線長度偏差(通常控制在幾十mil以內)。

-

地址/命令/控制(CA)總線與數據(DQ/DQS)總線同步: 需嚴格匹配CA總線與DQ總線的飛行時間差。

-

片上端接(ODT)優化: 合理配置ODT值以優化信號質量并降低功耗。

-

Vref穩定性: 接收端參考電壓(Vref)必須極其穩定和低噪聲。

-

電源噪聲抑制: 內存子系統對電源紋波極其敏感,需要極其干凈且響應快速的供電網絡(多層低阻抗平面、大量靠近芯片的去耦電容)。SMT貼片精度和焊接可靠性在此至關重要。

-

MIPI CSI-2/D-PHY/C-PHY:

-

應用: 連接高分辨率攝像頭模組的主流接口。

-

SI設計關鍵點:

-

高速串行差分對: D-PHY HS模式速率可達4.5Gbps/lane以上,C-PHY速率更高。需滿足嚴格的差分阻抗、對內偏移要求。

-

低功耗要求: LP(低功耗)模式信號質量同樣重要,影響通信可靠性。

-

短鏈路優化: 攝像頭鏈路通常較短,但連接器、FFC/FPC線纜的阻抗不連續點需重點優化。

-

共模噪聲抑制: 攝像頭常位于電磁環境復雜的區域,設計需關注共模噪聲的抑制。

-

車載傳統總線(CAN FD, FlexRay, LIN等):

-

應用: 與車輛其他ECU通信、控制執行器等。雖然速率相對不高,但功能安全要求極高。

-

SI設計關鍵點:

-

網絡拓撲與終端匹配: 正確的終端電阻匹配對防止反射、保證信號質量至關重要,尤其在FlexRay等高速差分總線上。

-

抗干擾能力: 設計需考慮在惡劣車載電磁環境下的魯棒性(如雙絞線使用、屏蔽設計)。

-

故障安全: 需考慮總線短路、開路等故障模式下的安全狀態。

-

SMT貼片與PCBA加工的關鍵作用:

-

高精度貼裝: 高速芯片(BGA、CSP封裝)的焊點間距極小,SMT貼片機的精度直接影響焊點質量和信號路徑的連續性。貼片偏移可能導致焊點橋連、虛焊,破壞信號完整性。

-

焊接質量: 回流焊溫度曲線控制不當會導致焊料潤濕不良、空洞、冷焊等問題,增加阻抗不連續點或導致開路/短路,嚴重影響高速信號傳輸。

-

元件共面性: 大型BGA或連接器的共面性差,會導致局部焊接不良,影響電源分配或信號連接。

-

材料一致性: PCBA加工中使用的焊錫膏、助焊劑的性能必須穩定可靠,避免殘留物引起漏電或腐蝕,影響長期可靠性。

-

工藝控制: 對阻抗控制走線的蝕刻精度、層壓對準度、鍍銅均勻性等PCBA加工核心工藝的嚴格控制,是確保設計階段SI仿真結果得以在實物上實現的基礎。

-

清潔度: 殘留的離子污染物在高濕環境下可能導致電化學遷移,造成短路或漏電,影響信號和電源完整性。

總結:

自動駕駛域控制器PCBA的信號完整性設計是一個涉及芯片、封裝、PCB設計、材料選擇、互連技術、SMT貼片及PCBA加工工藝的系統性工程。深入理解并嚴格滿足PCIe、高速以太網、LPDDR、MIPI等關鍵高速總線的電氣規范,并將其要求貫穿于從設計仿真到制造落地的每一個環節(特別是高精度制造工藝的控制),是打造高性能、高可靠、滿足功能安全要求的自動駕駛“大腦”的核心保障。在追求更高算力與更快傳輸速率的道路上,SI設計與精密制造工藝的協同優化將始終扮演至關重要的角色。

因設備、物料、生產工藝等不同因素,內容僅供參考。了解更多smt貼片加工知識,歡迎訪問深圳PCBA加工廠家-1943科技。

2024-04-26

2024-04-26