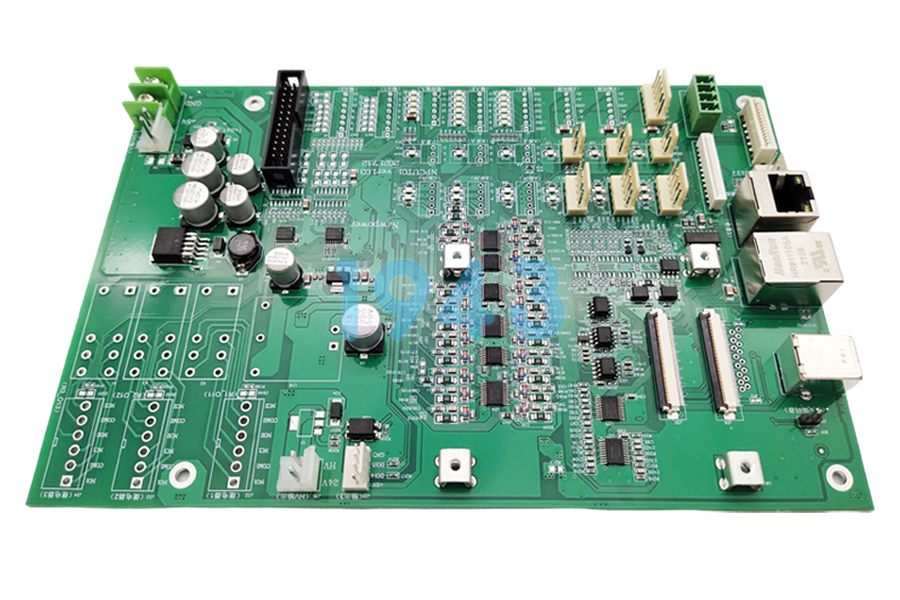

以下是針對工業 PLC 模塊 PCBA 實現微秒級實時信號傳輸延遲優化的技術方向梳理,結合硬件設計、協議優化、軟件架構及系統協同等維度:

一、硬件設計與信號完整性優化

-

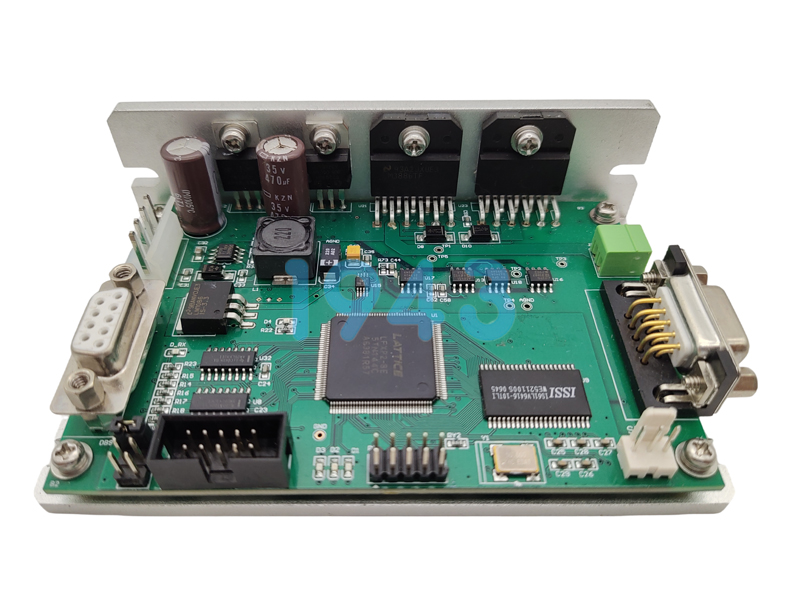

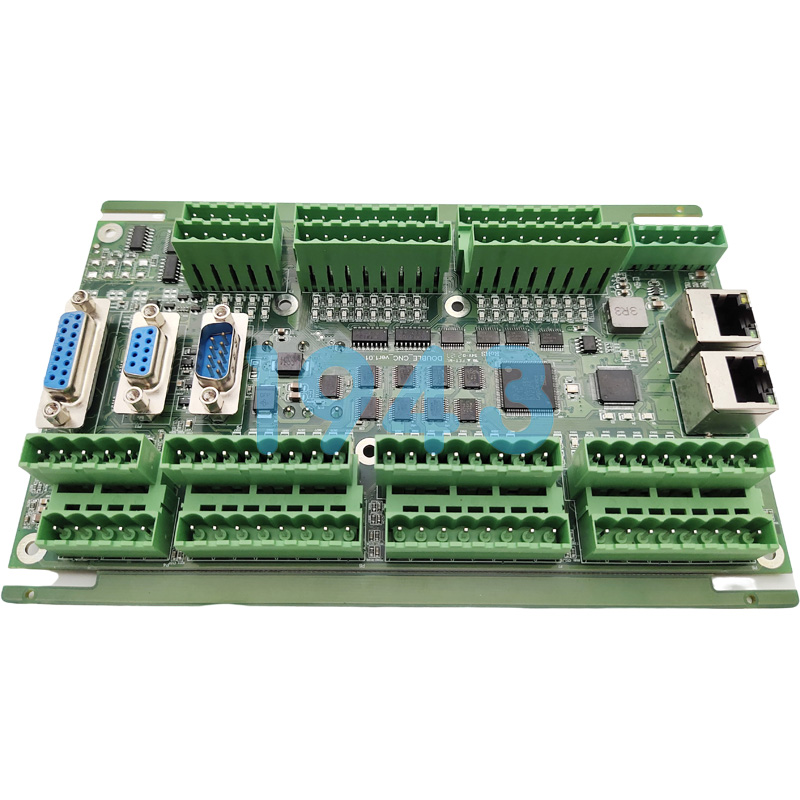

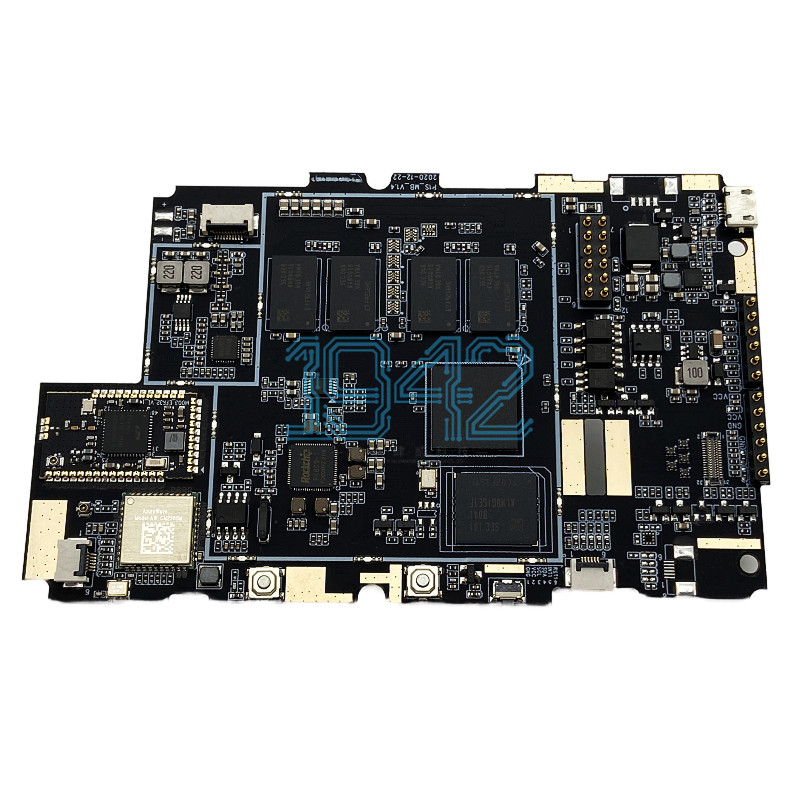

高速器件選型與接口匹配

- 采用低延遲微控制器(如 ARM Cortex-R 系列、專用實時控制芯片)與高速接口芯片(如支持 SERDES 的 FPGA/ASIC、EtherCAT 從站控制器 ESC)。

- 關鍵信號鏈路(如時鐘、同步信號、高速數據總線)匹配傳輸線阻抗(如 50Ω/90Ω 差分阻抗),減少信號反射與畸變。

-

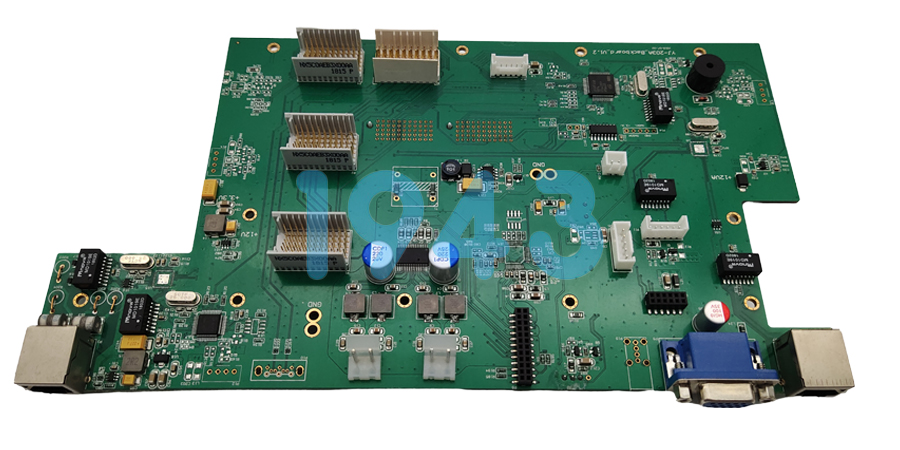

PCB 布局與布線策略

- 高速信號(如 LVDS、HDMI、工業以太網差分對)采用短路徑、少過孔設計,避免跨層交叉,優先使用內層帶狀線降低 EMI。

- 時鐘信號獨立隔離,差分對嚴格等長(誤差<5mil),電源層與地層緊密耦合,減少電源噪聲對信號的干擾。

-

硬件加速與緩存機制

- 集成硬件加速器(如專用通信協處理器、DMA 控制器)分擔 CPU 負載,實現數據零拷貝傳輸。

- 配置片上高速緩存(Cache)或片外 SRAM,減少主存訪問延遲,提升數據處理效率。

二、實時通信協議與鏈路優化

-

低延遲協議選擇與定制

- 采用實時以太網協議(EtherCAT、Profinet RT/IRT、Ethernet/IP CIP Sync)或專用總線(CAN FD、SERCOS III),支持微秒級循環周期。

- 定制輕量化應用層協議,精簡數據幀頭(如省略冗余校驗字段),減少協議解析開銷。

-

網絡架構與同步機制

- 星型 / 環型拓撲降低網絡跳數,配合交換機端口硬件時間戳(如 IEEE 1588 PTP 精確時鐘同步),實現亞微秒級時鐘同步精度。

- 硬件時間戳標記信號收發時刻,避免軟件中斷處理引入的延遲抖動。

三、軟件架構與實時性優化

-

實時操作系統(RTOS)與任務調度

- 選用確定性調度 RTOS(如 QNX、RTX、VxWorks),配置搶占式優先級調度,關鍵任務(如通信中斷處理)設為最高優先級,禁止不必要的任務切換。

- 最小化中斷服務程序(ISR)執行時間,將數據處理移至后臺任務(Task),減少中斷嵌套深度。

-

驅動與協議棧優化

- 硬件驅動采用輪詢(Polling)與中斷結合模式,對高速數據鏈路(如以太網)使用零拷貝技術(Zero-Copy)避免數據復制延遲。

- 協議棧內核態實現,減少用戶態 - 內核態上下文切換,或通過 FPGA 硬邏輯實現部分協議處理(如 CRC 校驗、數據成幀)。

-

算法與數據處理輕量化

- 避免動態內存分配(如使用靜態內存池),數據預處理在硬件層面完成(如 ADC 采樣直接存入 DMA 緩沖區)。

- 采用高效數據結構(如環形緩沖區)減少數據拷貝,對實時信號禁用浮點運算,轉為定點數處理降低計算延遲。

四、系統級協同與驗證

-

端到端延遲建模與仿真

- 使用信號完整性仿真工具(如 HyperLynx、Cadence Sigrity)預測 PCB 布線延遲,結合時序分析工具(如 Synopsys PrimeTime)評估芯片內部流水線延遲。

- 構建硬件在環(HiL)測試平臺,模擬工業現場環境(如高溫、振動)下的延遲穩定性。

-

同步與抖動抑制

- 外部輸入同步信號(如 10MHz 參考時鐘)經鎖相環(PLL)倍頻生成系統時鐘,減少時鐘抖動對信號采樣的影響。

- 對異步通信接口(如 UART)增加 FIFO 緩沖,平滑數據輸入輸出速率差異。

-

量產一致性控制

- 關鍵器件(如晶振、PHY 芯片)篩選頻率偏差<50ppm,回流焊后校準時鐘偏移,確保模塊間延遲一致性。

- 自動化測試設備(ATE)批量測量信號環路延遲(如發送 - 接收時間差),剔除超標的 PCBA。

五、環境適應性與可靠性

- 溫度補償:針對工業寬溫(-40℃~+85℃)場景,通過溫度傳感器實時調整時鐘頻率補償器件延遲漂移。

- EMC 強化:接口端增加 ESD 保護器件(如 TVS 二極管)、共模電感濾除高頻噪聲,避免干擾導致的重傳與延遲波動。

通過上述多維度技術協同,可將工業 PLC 模塊 PCBA 的端到端信號傳輸延遲控制在微秒級,滿足高精度實時控制(如運動伺服、過程同步)的嚴苛需求。

因設備、物料、生產工藝等不同因素,內容僅供參考。了解更多smt貼片加工知識,歡迎訪問深圳smt貼片加工廠-1943科技。

2024-04-26

2024-04-26